硬件描述语言程序,深入浅出Verilog硬件描述语言程序设计

时间:2024-10-08 来源:网络 人气:

深入浅出Verilog硬件描述语言程序设计

随着电子技术的飞速发展,硬件描述语言(HDL)已成为现代电子系统设计的重要工具。Verilog作为一种广泛使用的硬件描述语言,在数字电路设计、FPGA开发等领域发挥着重要作用。本文将深入浅出地介绍Verilog程序设计的基本概念、语法结构以及设计方法。

一、Verilog简介

Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。它允许设计者以文本形式描述电子系统的行为和结构,从而实现电路的仿真、综合和测试。Verilog不仅适用于FPGA设计,也广泛应用于ASIC(应用特定集成电路)的开发中。

二、Verilog基本语法

Verilog的语法结构对于初学者来说可能有些陌生,但一旦掌握,它将极大地提高设计效率。以下是Verilog编程的基础元素:

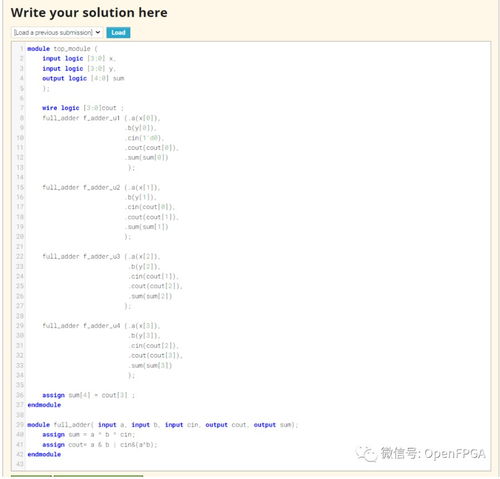

1. 模块定义

模块是Verilog程序的基本单位,它定义了电路的一部分或全部功能。模块定义通常包含以下内容:

模块名称

端口定义

信号类型声明

逻辑功能定义

2. 运算符与表达式

Verilog提供了丰富的运算符和表达式,用于对信号进行数学和逻辑运算。主要包括以下几种:

算术运算符

逻辑运算符

位运算符

关系运算符

3. 语句

Verilog语句用于描述数字电路的行为和功能,包括以下几种:

赋值语句

块语句

条件语句

循环语句

三、Verilog程序设计方法

Verilog程序设计方法主要包括以下几种:

1. 顶层模块设计

顶层模块是整个系统的入口,它负责将各个子模块连接起来,实现整个系统的功能。在设计顶层模块时,需要考虑以下因素:

模块之间的接口

模块之间的时序关系

模块之间的资源分配

2. 子模块设计

子模块是构成顶层模块的基本单元,它负责实现特定的功能。在设计子模块时,需要考虑以下因素:

模块的功能描述

模块的输入输出端口

模块的内部逻辑结构

3. 仿真与测试

仿真与测试是Verilog程序设计的重要环节,它可以帮助设计者验证电路的功能和性能。在设计过程中,可以通过以下方法进行仿真与测试:

创建测试平台

编写测试向量

运行仿真

分析仿真结果

Verilog作为一种强大的硬件描述语言,在数字电路设计、FPGA开发等领域具有广泛的应用。通过掌握Verilog的基本语法和设计方法,可以有效地提高设计效率,缩短设计周期。本文对Verilog程序设计进行了简要介绍,希望对初学者有所帮助。

相关推荐

教程资讯

教程资讯排行

- 1 小米平板如何装windows系统,轻松实现多系统切换

- 2 迅雷敏感文件无法下载,迅雷敏感文件无法下载?教你轻松解决

- 3 信息系统集成费标准,费用构成与计算方法

- 4 怎样将windows系统下载到u盘里,随时随地使用

- 5 魔百盒cm101s系统升级,2023移动魔百盒cm101s破解刷机固件下载

- 6 重装系统进入windows卡住,原因排查与解决攻略

- 7 小米平板4能装成windows系统,兼容性与操作指南

- 8 ps3破解系统升级4.76,操作指南与注意事项

- 9 海湾多线模块接线图,海湾多线模块接线图详解

- 10 360软件管家下载的东西在哪,360软件管家下载的东西在哪里?全面解析下载文件存放位置