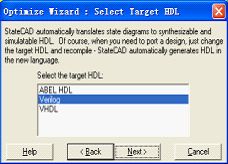

硬件描述语言verilog,硬件描述语言的魅力与运用

时间:2024-09-29 来源:网络 人气:

深入浅出Verilog:硬件描述语言的魅力与运用

在电子设计领域,硬件描述语言(HDL)已成为设计复杂电子系统不可或缺的工具。Verilog作为其中一种主要的HDL,因其简洁的语法和强大的功能而受到工程师的青睐。本文将深入浅出地介绍Verilog,帮助读者了解其魅力与运用。

一、Verilog简介

Verilog是一种硬件描述语言,用于描述数字系统硬件的结构和行为。它允许设计者以文本形式描述电子系统的行为和结构,从而实现数字电路的设计、仿真和综合。Verilog不仅用于FPGA(现场可编程门阵列)的设计,也广泛应用于ASIC(应用特定集成电路)的开发中。

二、Verilog的历史与发展

Verilog语言最早由Philip A. Moorby和Gary D. Pettis于1983年开发,目的是简化数字电路的设计过程。随后,它被标准化为IEEE 1364-1985标准,并在1995年更新为IEEE 1364。经过多年的发展,Verilog已成为电子设计自动化(EDA)领域的核心语言之一。

三、Verilog的基本语法

Verilog的语法类似于C语言,包括变量声明、数据类型、运算符、控制语句等。以下是一些基本语法示例:

变量声明:reg a; wire b;

数据类型:integer, real, logic等

运算符:+、-、、/、==、&、|等

控制语句:if、case、for、while等

四、Verilog模块与端口

Verilog中的模块是设计的基本单元,用于描述电路的功能。每个模块都包含输入端口和输出端口。以下是一个简单的模块示例:

```verilog

module my_module (

input clk,

input reset,

output reg out

always @(posedge clk or posedge reset) begin

if (reset) begin

out <= 0;

end else begin

out <= 1;

end

endmodule

五、组合逻辑与时序逻辑

Verilog中的组合逻辑与时序逻辑是两种基本的设计方法。组合逻辑的输出仅取决于当前输入,而时序逻辑的输出不仅取决于当前输入,还取决于之前的输入和输出。以下是一个组合逻辑的示例:

```verilog

module and_gate (

input a,

input b,

output y

assign y = a & b;

endmodule

六、时钟域与同步设计

在数字电路设计中,时钟域和同步设计至关重要。Verilog提供了多种同步设计方法,如时钟使能、时钟域交叉等。以下是一个时钟使能的示例:

```verilog

module clock_enable (

input clk,

input enable,

output reg out

always @(posedge clk) begin

if (enable) begin

out <= 1;

end else begin

out <= 0;

end

endmodule

七、Verilog高级特性

Verilog具有许多高级特性,如任务、函数、多维数组、结构体和系统函数等。以下是一个任务的示例:

```verilog

task my_task (

input [3:0] a,

output [3:0] b

begin

b = a + 1;

endtask

八、Verilog编码风格与最佳实践

良好的编码风格和最佳实践对于Verilog设计至关重要。以下是一些常见的编码风格和最佳实践:

命名规范:使用有意义的变量和模块名称

模块化设计:将设计分解为多个模块,提高可重用性和可维护性

注释:添加注释以解释代码的功能和设计思路

Verilog作为一种强大的硬件描述语言,在电子设计领域具有广泛的应用。通过本文的介绍,相信读者对Verilog有了更深入的了解。掌握Verilog,将为你的电子设计之路增添更多可能性。

教程资讯

教程资讯排行