verilog硬件描述语言,从入门到精通

时间:2024-10-03 来源:网络 人气:

深入浅出Verilog硬件描述语言:从入门到精通

在数字电路设计领域,硬件描述语言(HDL)是工程师们不可或缺的工具。Verilog HDL作为一种广泛使用的硬件描述语言,因其简洁的语法和强大的功能而受到工程师的青睐。本文将带领您从入门到精通,深入了解Verilog硬件描述语言。

一、Verilog HDL简介

Verilog HDL,全称为Verilog Hardware Description Language,是一种用于描述数字系统硬件结构和行为的文本语言。它被广泛应用于数字电子系统的描述、仿真和综合。Verilog HDL的语法自由、易学易用,支持算法级、门级设计,代码简洁,发展迅速。

二、Verilog HDL的历史与发展

Verilog语言最早由Philip A. Moorby和Gary D. Pettis于1983年开发,目的是简化数字电路的设计过程。随后,它被标准化为IEEE 1364-1985标准,并在1995年更新为IEEE 1364。经过多年的发展,Verilog已成为电子设计自动化(EDA)领域的核心语言之一。

三、Verilog HDL的基本语法

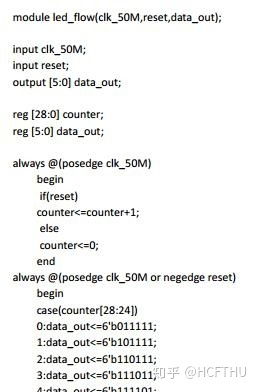

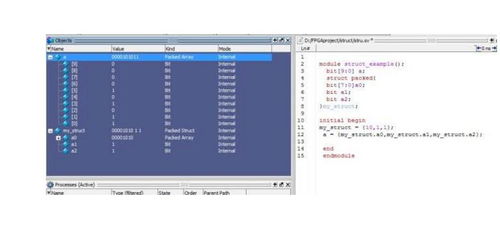

Verilog HDL的语法与C语言类似,但也有一些本质的区别。以下是一些基本的语法元素:

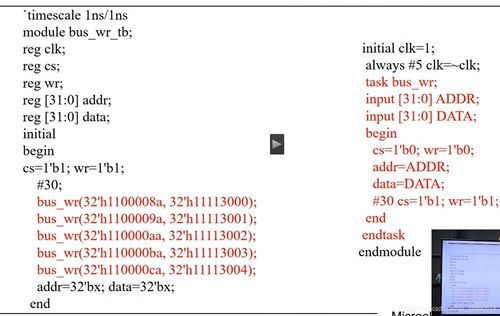

模块(Module):Verilog HDL中的基本单元,用于描述电路的功能。

端口(Port):模块的输入和输出接口。

数据类型:包括整数、实数、逻辑等。

连续赋值语句:用于描述电路的时序特性。

过程块:用于描述电路的行为特性。

四、Verilog HDL的设计方法

Verilog HDL的设计方法主要包括以下几种:

行为级设计:描述电路的功能特性。

结构级设计:描述电路的组成结构。

门级设计:描述电路的硬件实现。

五、Verilog HDL的仿真与验证

Verilog HDL的仿真与验证是设计过程中的重要环节。以下是一些常用的仿真与验证方法:

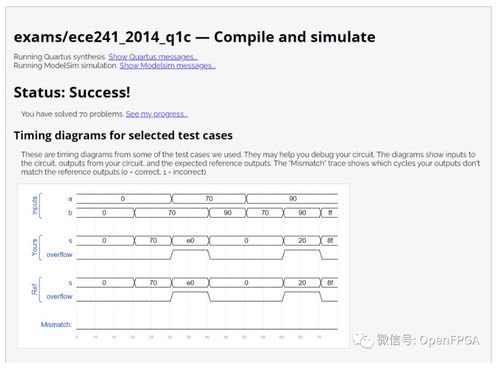

功能仿真:验证电路的功能是否正确。

时序仿真:验证电路的时序特性是否满足要求。

波形分析:分析电路的波形,了解电路的工作过程。

六、Verilog HDL的应用场景

Verilog HDL的应用场景非常广泛,主要包括以下几方面:

IC设计:用于设计复杂的数字集成电路。

FPGA开发:用于设计FPGA上的数字电路。

嵌入式系统:用于设计嵌入式系统的数字电路。

系统级仿真:用于仿真整个电子系统。

七、Verilog HDL的未来发展趋势

随着数字电路设计的日益复杂,Verilog HDL将继续发展,以下是一些未来发展趋势:

支持更高层次的抽象设计。

提高仿真速度和精度。

支持更多硬件加速技术。

Verilog HDL作为一种强大的硬件描述语言,在数字电路设计领域发挥着重要作用。通过本文的介绍,相信您对Verilog HDL有了更深入的了解。希望您在今后的学习和工作中,能够熟练运用Verilog HDL,设计出优秀的数字电路。

相关推荐

- 装错windows系统了怎么办,装错Windows系统了怎么办?快速解决指南

- 最推荐的windows版本系统,最推荐的Windows版本系统——深度解析与选择指南

- 系统改英语windows10

- 台式电脑windows系统,全面解析与安装指南

- 系统卡为什么windows10,windows10很卡反应很慢该如何处理

- 怎样从windows中恢复系统,如何从Windows中恢复系统

- 移动windows10系统

- 新系统激活windows10,电脑右下角显示激活windows怎么去掉

- 在哪下windows系统好,如何选择可靠的Windows系统下载平台

- 微软windows8系统游戏,创新体验与兼容性的完美结合

教程资讯

教程资讯排行

- 1 迅雷敏感文件无法下载,迅雷敏感文件无法下载?教你轻松解决

- 2 ps3破解系统升级4.76,操作指南与注意事项

- 3 魔百盒cm101s系统升级,2023移动魔百盒cm101s破解刷机固件下载

- 4 信息系统集成费标准,费用构成与计算方法

- 5 华硕x550v系统升级,轻松提升电脑性能

- 6 中国电信在线投诉平台,中国电信在线投诉平台——您的权益守护者

- 7 海湾多线模块接线图,海湾多线模块接线图详解

- 8 dpos订货系统,提升供应链效率的数字化解决方案

- 9 可穿戴设备 英文,Iroducio o Wearable Devices

- 10 xp电脑开机后进不了系统,XP电脑开机后进不了系统的常见原因及解决方法